# **BMC 076. 4HP Common Input Logic Gates Build Documentation.**

I. Using The Module

II. Schematic

III. Construction

A. Parts List B. PCB Layout

#### I. Using The Module.

This module provides three logic gates that share a single input. By swapping CMOS logic chips the gates can be set up as AND, OR, XOR, NAND, NOR or XNOR. It outputs +5V gates and accepts any signal as an input.

I've found it most useful when used as an AND gate, applying a clock to the common input to synchronize timing signals.

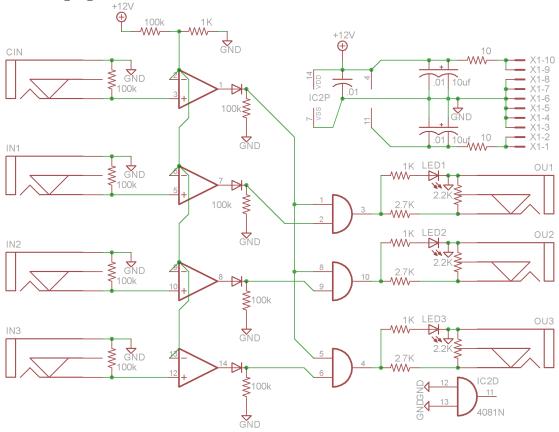

#### II. Schematic.

Above is the schematic for this module. Starting at the left, each input has a 100K resistor to ground and then connects to a comparator. Each comparator's threshold is set at .012V by the 100K/1K voltage divider at the top of the schematic. Each comparator's output goes through a switching diode to only allow positive voltages and then connects to a 100k resistor to ground which grounds the signal when no current flows through the diode.

These outputs then connect to the inputs of the logic gates, an AND is shown in the schematic. The output of each gate connects to an LED through a 1K current limiting resistor and then to the output jack through a 2.7K/2.2K resistor voltage divider that attenuates the +12V output of the gate down to +5V. The inputs of the unused gate are grounded.

At the top right are the power connectors. The positive and negative voltage rails are low pass filtered by a 10ohm/10uf RC pair. Additional .01uf capacitors are placed near the power pins of the ICs. The TL074 is connected to the positive and negative voltage rails, while the logic gate IC is connected to the positive rail and ground.

# **III. Construction**

## A. Parts List

## Semiconductors

| Value           | Quantity | Notes                          |

|-----------------|----------|--------------------------------|

| TL074           | 1        | 14 pin DIP                     |

| CMOS Logic chip | 1        | 14 pin DIP, see table below    |

| 1N4148          | 4        | Or other small switching diode |

| LED             | 3        | 3mm through hole               |

| LOGIC FUNCTION | Chip to use |  |

|----------------|-------------|--|

| AND            | CD4081      |  |

| OR             | CD4071      |  |

| XOR            | CD4030      |  |

| NAND           | CD4011      |  |

| NOR            | CD4001      |  |

| XNOR           | CD4077      |  |

#### Resistors

| 1105151015 | 1100101010 |                                                     |  |

|------------|------------|-----------------------------------------------------|--|

| Value      | Quantity   | Notes                                               |  |

| 10 ohm     | 2          | 5mm lead spacing. Use 3.5mm body length or stand up |  |

| 1Kohm      | 5          | " "                                                 |  |

| 2.2K ohm   | 3          | " "                                                 |  |

| 2.7K ohm   | 3          | " "                                                 |  |

| 100 Kohm   | 9          | " "                                                 |  |

Capacitors

| Value | Quantity | Notes                                  |

|-------|----------|----------------------------------------|

| .01uf | 3        | Small ceramic disc. Value not critical |

| 10uf  | 2        | Electrolytic                           |

## Other/Off Panel

| Value             | Quantity | Notes                                              |

|-------------------|----------|----------------------------------------------------|

| Power connecter   | 1        | Right angle 2x5 2.54mm, <u>like this.</u>          |

| Jacks             | 7        | PCB is designed around these jacks: <u>PJ-323M</u> |

| 14 pin DIP Socket | 2        |                                                    |

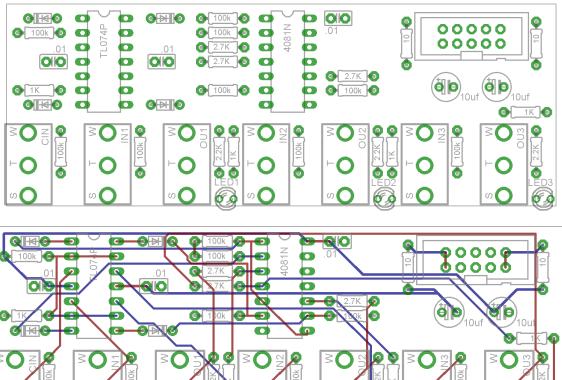

#### **B. PCB Layout**

Below are renderings of the PCB. The rendering showing the traces does not show the ground fill plane, so assume any missing connection is a ground fill.

The PCB measures 97mm x 36mm and the jacks are spaced 14mm apart.

This is a photo of a completed module

**σ**